# **Mosaic Microsystems Ultra-Thin Glass Solutions**

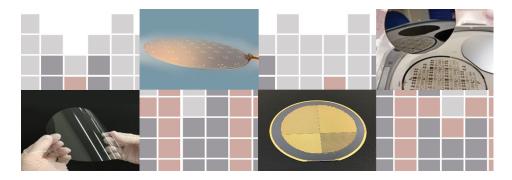

Mosaic Microsystems provides ultra-thin glass-based packaging and integration solutions for advanced microelectronics and photonics applications. Mosaic's glass technology leverages the superior material properties of glass with substrate thicknesses down to 70  $\mu$ m and through-glass via (TGV) diameters of 30  $\mu$ m. Standard types of glass are alumino-borosilicate glass (ABS) (CTE match to Si), and fused silica (FS) (ultra-low loss). The advantages of glass include superior mechanical and electrical properties, stability over a wide range of environmental conditions, and compatibility with semiconductor processing providing enhanced performance over existing solutions particularly at frequencies above 3 GHz. Applications include 5G wireless, radar, photonics, interposers, MEMS and sensors.

#### Viaffirm™ Bond Technology

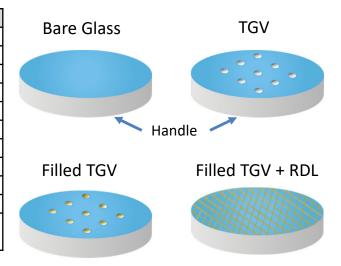

Glass thinner than 250 µm is normally difficult to handle in a semiconductor manufacturing facility. Mosaic offers a solution which involves temporarily bonding the glass to a handle wafer, which is typically silicon. Viaffirm™ is inorganic, can be processed in high vacuum systems and at temperatures up to 450 °C. It is easily debonded using standard mechanical methods. The result is the ability to leverage semiconductor manufacturing processes to create precision features that include substrate integrated waveguides, passive devices and fine L/S circuitry.

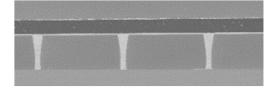

#### **Through-Glass Vias**

Mosaic's TGV technology allows for the formation of vias 30  $\mu m$  in diameter. The vias can be filled with metals to enable heterogeneous integration. Multiple metal layers can be formed on either side and semiconductor die can be directly bonded to the glass using BGA or metal compression bonding.

## **Material properties**

## Wafers provided at four levels of integration

| Property                                               | BSG                 | FS                            |  |  |

|--------------------------------------------------------|---------------------|-------------------------------|--|--|

| Dielectric Constant                                    | 5.25                | 3.79                          |  |  |

| Loss Tangent @10 GHz                                   | 0.006               | 0.0002                        |  |  |

| Loss Tangent @ 69 GHz                                  | 0.009               | 0.0004                        |  |  |

| DC Resistivity (Log <sub>10</sub> $\Omega$ -cm 250 °C) | 12.9                | 15                            |  |  |

| Refractive Index @ 589 nm                              | 1.51                | 1.46                          |  |  |

| CTE (ppm/°C)                                           | 3.2                 | 0.5                           |  |  |

| Thermal Conductivity (W/cm-°K)                         | 0.019               | 0.014                         |  |  |

| Density (g/cm³)                                        | 2.38                | 2.2                           |  |  |

| Young's Modulus (GPa)                                  | 73.6                | 73                            |  |  |

| Poisson's Ratio                                        | 0.23                | 0.16                          |  |  |

| Hardness                                               | H <sub>v</sub> =640 | H <sub>k</sub> =522<br>kg/mm² |  |  |

# **Wafer Specifications**

| Property                         | ABS               |         |      |          | FS        |           |         |           |          |  |  |

|----------------------------------|-------------------|---------|------|----------|-----------|-----------|---------|-----------|----------|--|--|

| Wafer Diameter <sup>1</sup> (mm) | 99                | 149     | 19   | 99       | 299       | 99        | 149     |           | 199      |  |  |

| Alignment Features               | Flat              | Flat    | No   | tch      | Notch     | Flat      | Flat    | lat Notch |          |  |  |

|                                  | 18, 32.5 mm       | 57.5 mm | SE   | MI       | SEMI      | 32.5 mm   | 57.5 mm | 5 mm SEMI |          |  |  |

| Handle Wafer Material            | Si                |         |      |          | FS        |           |         |           |          |  |  |

| Glass Thickness w/o TGV (μm)     | 70, 100, 125, 200 |         |      |          |           | 100 - 200 |         |           |          |  |  |

| Glass Thickness w/ TGV           | 100               |         |      |          | 100 - 150 |           |         |           |          |  |  |

| Surface Roughness (nm Ra)        | <1                |         |      |          |           | <1        |         |           |          |  |  |

| TTV (µm)                         | < 5               |         |      |          |           | <10       |         |           |          |  |  |

| Via Diameter <sup>2</sup> (um )  | Тор               |         |      | Bottom   |           | Тор       |         | Bottom    |          |  |  |

|                                  | 30 +/- 3          |         |      | 23 +/- 3 |           | 30 +/- 3  |         | 23 -      | 23 +/- 3 |  |  |

| Viaffirm Bond                    |                   |         |      |          |           |           |         |           |          |  |  |

| Bond Energy (mJ/m²)              | Low               | Std.    | Std. |          | High      |           | Sto     | ł.        | High     |  |  |

|                                  | ≤300              | 400     |      | ≥700     |           | ≤300      | 40      | 0         | ≥700     |  |  |

| Voids (%area)                    | <1.5%             |         |      |          | <1.5%     |           |         |           |          |  |  |

#### Notes:

- 1. Glass wafers are typically undersized by 1mm to accommodate handling, full size glass wafers available upon request.

- 2. Via diameters 15 35 um and in glass thickness < 100 um and up to 175 um thick are in development.

- 3. Edge exclusion of 5 10 mm is typical.

Please contact us to discuss your metallization or wafer needs not described above, including 300 mm!

https://www.mosaicmicro.com/contact-us/